はじめに

ZYBO購入後,最初にZYBO Base System Designをやってみました. ZYBO Base System Designは,Digilentが配布しているリファレンスプロジェクトのようです. 下記ページにてダウンロードできます.

他に参考にしたWebページは,marsee氏の「FPGAの部屋」です. ZYBO Base System DesignにはVivado 2013.4用のプロジェクトファイルが付属していますが,marsee氏はVivado 2014.1を使用されていたので,私はVivado 2014.4でやってみることにしました.

事前準備

microSDHCのフォーマット

購入したmicroSDHCカードをフォーマットしておきました. 「デバイスの既定値を復元する」をクリックした後,クイック フォーマットを実行しました.

ドライバのインストール

UARTに必要なドライバをインストールしておきました.

Tera Termのインストール

Tera Termなどのターミナルソフトウェアが必要になります. 私はインストール済みでしたので,設定のみ変更しました.

作業備忘録

- プロジェクトディレクトリを準備する 「zybo_base_system.zip」を展開し,できるだけ浅い階層のディレクトリにファイルを置きます. Windowsはファイルパスに文字数制限がありますが,Vivadoがディレクトリを自動生成する際に,この制限を超過しないようにするためです. 私は,「C:\work\zybo_base_system」に,展開してできたディレクトリの「source\vivado\」以下のファイル(「hw」および「SDK」)を移動しました.

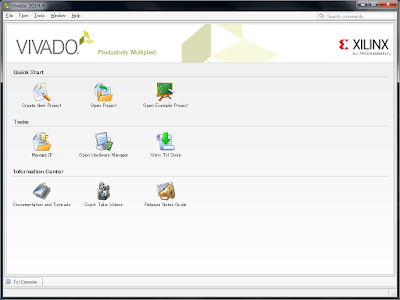

- Vivadoを起動する

- プロジェクトを開く 「Open Project」から「C:\work\zybo_base_system\hw\zybo_bsd\zybo_bsd.xpr」を開きます. 下図のようなウィンドウが開きますので,「Automatically upgrade ...」を選択して「OK」をクリックします. 「Default Library」ウィンドウも表示されましたが,「OK」をクリックしました.

- Upgrade IP 「Project Upgraded」ウィンドウが開きますので,「Report IP Status」をクリックしました. 「Upgrade Selected」をクリックしました. 「OK」をクリックしました. Critical Warningが出ましたが無視しました. 以降の「Generate Block Diagram」でもCritical Warningが出ましたが,同様に無視しても問題はありませんでした.

- Generate Block Diagram 「Flow Navigator」の「IP Integrator」 - 「Generate Block Diagram」を実行しました.

- Generate Bitstream 「Flow Navigator」の「Program and Debug」 - 「Generate Bitstream」を実行しました. エラーなく,Bitstreamを生成できました.

0 件のコメント:

コメントを投稿